Logic design entries: VHDL, Veilog, AHDL, Graphic

TECHNICAL EXPERTISE

Product 6

The objective of this project is measuring the position of the wafer, indicating its exact contours.

The precision is 13 micrometers (μm or 10−6 meter).

Product 1

The board was designed and produced by Elik-tronics for Applied Materials.

It consists of 12 FPGAs and 4 CPLDs.

It is used to process an image from a line scan camera.

It consists of 12 FPGAs and 4 CPLDs.

It is used to process an image from a line scan camera.

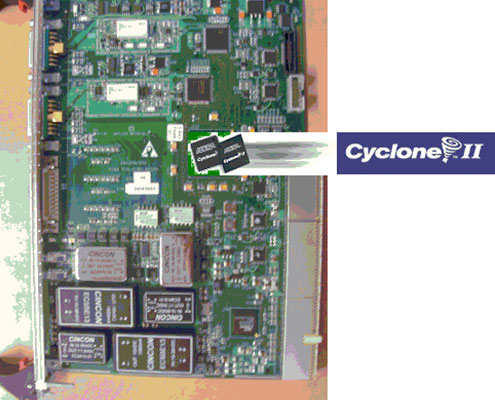

Product 2

The board consists of an FPGA CyclonII EP2C35 (migrated to C50) designed by Elik-tronics,

2 fast analog channels sampled in 220Mhz ADCs and entered (12 bits LVDS) into the CycloneII.

The CycloneII processes the data, using arithmetics and true dual-port rams.

Many different modes of operations (data ordering etc.) are used, including diagnostic mode

(which injects pattern generator data to the input).

We achieve a high work frequency of 240Mhz in CycloneII .

The output is full camera link 5.5Gbps.

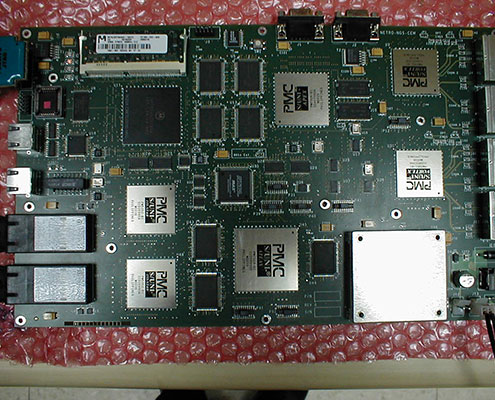

Product 3

The board on the left was produced by Elik-tronics for a broadband fixed wireless

access system. It consists of an ATM Layer (S/UNI ALTLASPMC Sierra) and S/UNI VERTEX

chip set from PMC Sierra - the processor is POWERQUICC MPC8260 (Motorola).

The card provides ATM traffic policing (S/UNI-ATLAS),

ATM cell traffic management (S/UNI-APEX) and ATM cell multiplexing.

The CEM communicates with the other line cards (designed by Elik-tronics as well)

via the serial LVDS lines using the PMC protocol (S/UNI-VORTEX and S/UNI-DUPLEX).

On the network side, the card interfaces via two optical transceivers-2x STM1/OC3c interfaces.

Product 4

The board on the left was designed by Elik-tronics ALLOT Communication.

It consists of 2x10Gb XFP interfaces , 2 x SerDeses (Vitesse) interfaces with 2x MACs

(Vitesse) with XAUI protocol.

The MAC's output is 2x SPI4.2 interfaces to connectors.

Elik-tronics also designed the CPLD (MaxII)m which controls all the peripherals.

Product 5

This board was designed and produced by Elik-tronics for cPCI wide cage.

It consists of Xilinx Vertex-5 (110T), 12 Channel optical links (Rx and Tx for testing)

600 Mhz DDR2 interface (with SODIM), four full camera link fast interfaces.

The Virtex-5 uses 12 internal GTPs and performs about 36 Gbps.

Optical transceivers are Zarlink (cross-ref with Agilent and Picolight).

All the fast serial links have been tested for zero BER.